[ad_1]

Intel is set to present a couple of papers next week, detailing the progress for two of its transistor technologies: the Gate-All-Around (GAA) RibbonFET and PowerVia. Of the two, the latter is expected to serve as the blue chipmaker’s one-two punch delivery, primarily due to the fact that it will be talking about the implementation of new technology with it, called Backside Power Delivery Network (BS-PDN).

As to what BS-PDN is, here’s a quick primer: as explained by Ryan Smith from Anandtech, the PowerVia Backside Power Delivery Network is a technology concept that Intel has been quietly researching for the past several years. In essence, its development is similar to the EUV application, but the difference here is that, moving forward, Intel may actually pave the way for other chip fabs to use this technology in the near and immediate future.

As to how PowerVia BS-PDN works, here’s a condensed version of the process: typically, a modern, processor with frontside power delivery has anywhere between 10 and 20 metal layers in its design. With the upcoming Intel 4 process, the processor will have 16 layers for logic, plus two “giant metal” layers on top for power routing and placing external connectors. The problem with frontside power delivery, though, is that signals on the chip actually have to travel through the layers before reaching the transistors, since they are on the same side of the chip. With backside power delivery, Intel is effectively separating those signals by moving all the power connections of the chip to the other side of the wafer.

With PowerVia BS-PDN, Intel uses something called Nano TSV. The “TSV” stands for through-silicon via, and it is basically designed to deliver power straight to a processor’s M0 layer, rather that having the power pass through it. Essentially, it is the concept of stacking multiple layers of silicon on top of the main die. Of course, if this all sounds familiar to some of you, it’s because you may have already heard of a similar concept from AMD and its 3D V-Cache technology. The main difference between the two technologies being that Nano TSVs are approximately 500 times smaller than typical TSVs. Another significant improvement is a 30% reduction in voltage droop, meaning that the processor could operate at lower voltages while still providing performance uplifts.

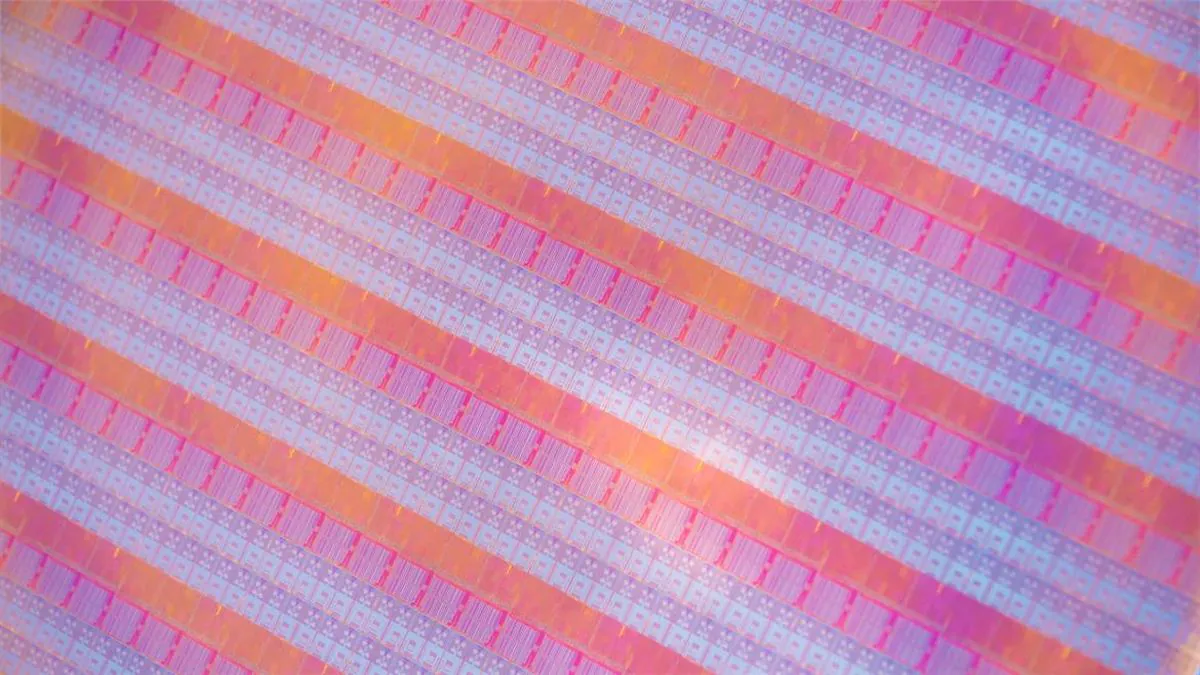

Additionally, Intel also announced that PowerVia with its BS-PDN is already working and that test chips exist – they’re officially known as “Blue Sky Creek” – made using a modified version of its Intel 4 process, which recently entered its mass production stage. If the technology does become a success, it would also be a bragging right for Intel, considering none of its competitors are expected to have their own variation of backside power delivery up and ready by 2026.

(Source: Anandtech, Hot Hardware)

Follow us on Instagram, Facebook, Twitter or Telegram for more updates and breaking news.

[ad_2]